Tag: computational memory

A Computational Memory Architecture for MPEG-4 Applications with Mobile Devices

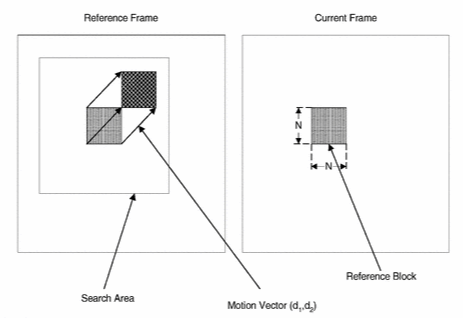

This paper presents a Computational Memory architecture for MPEG-4 applications with mobile devices. The proposed architecture is used for real-time block-based motion estimation, which is the most computational intensive task in the video encoder. It uses the exhaustive block-matching algorithm (EBMA) for motion estimation. The proposed architecture consists of embedded SRAMs and a number of block-matching units working in parallel to process video data while stored in the memory. The block-matching units access the embedded SRAMs simultaneously, which increases the speed of the architecture.

The architecture processes CIF format video sequences (i.e., the frame size is 352 × 288 pixels) with block size of 16 × 16 pixels and ±15 pixels search range. The proposed architecture has been designed, prototyped, and simulated for 0.18 μm TSMC CMOS technology. The simulation shows that the proposed architectures processes up to 126 CIF frames per second with clock frequency 100 MHz. The synthesized prototype of the proposed architecture includes 200 KB memory and it has an area of 33.75 mm2 and consumes 986.96 mW @100 MHz.

Mohammed Sayed , Wael Badawy, “A Computational Memory Architecture for MPEG-4 Applications with Mobile Devices,” Journal of VLSI Signal Processing Systems for Signal, Image and Video Technology – Special Issue on Digital and Computational Video , Vol. 42, No. 1, pp. 35-42, January 2006.