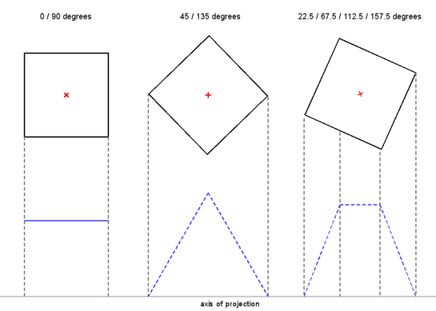

Architectures for Finite Radon Transform

Two VLSI architectures for the finite Radon transform are presented. The first is a reference architecture using memory blocks and the second is a memoryless architecture. The proposed architectures use 7×7 size image blocks and are prototyped for processing the CIF image sequence. The simulation and synthesis results show that the core speeds of the two proposed architectures are around 100 and 82 MHz, respectively.

Published in:

Electronics Letters (Volume:40 , Issue: 15 )

- Page(s):

- 931 – 932

- ISSN :

- 0013-5194

- INSPEC Accession Number:

- 8068176

- DOI:

- 10.1049/el:20040566

- Date of Publication :

- 22 July 2004

- Date of Current Version :

- 02 August 2004

- Issue Date :

- 22 July 2004

- Sponsored by :

- Institution of Engineering and Technology

- Publisher:

- IET

C. A. Rahman and W. Badawy, “Architectures for Finite Radon Transform“, The IEE Electronics Letters, Vol. 40, Issue 15, July 2004, pp. 931-932.

A Computational RAM (C-RAM) Architecture for Real-Time Mesh-Based Video Motion Tracking: Part II Motion Compensation

This paper presents a new Computational-RAM (C-RAM) architecture for real-time mesh-based video motion tracking. In Part 1, the motion estimation part of the proposed architecture is presented. Here in Part 2, a new C-RAM mesh-based motion compensation architecture is presented. The input data to the architecture is the mesh nodes motion vectors and the reference frame and the output data is the compensated (i.e., predicted) frame. The architecture uses the affine transformation for warping the deformed patches in the reference frame into the undeformed patches in the current frame. The architecture computes the affine parameters using a multiplication-free algorithm. The reference and current frames are stored in embedded S-RAMs generated with Virage™ Memory Compiler. The proposed motion compensation architecture has been prototyped, simulated and synthesized using the TSMC 0.18 μm CMOS technology. Using 100 MHz clock frequency, the proposed architecture processes one CIF video frame (i.e., 352×288 pixels) in 0.59 ms, which means it can process up to 1694 frames per second. The core area of the proposed motion compensation architecture is 28.04 mm2 and it consumes 31.15 mW.

Mohammed Sayed and Wael Badawy, “A Computational RAM (C-RAM) Architecture for Real-Time Mesh-Based Video Motion Tracking: Part II Motion Compensation,” Journal of Circuits, Systems and Computer, Vol. 13, Issue 6, December 2004, pp. 1217-1232.

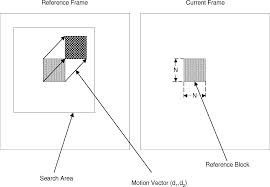

A Computational RAM (C-RAM) Architecture for Real-Time Mesh-Based Video Motion Tracking: Part I Motion Estimation,

This paper presents a new Computational-RAM (C-RAM) architecture for real-time mesh-based video motion tracking. The motion tracking consists of two operations: mesh-based motion estimation and compensation. The proposed motion estimation architecture is presented in Part 1 and the proposed motion compensation architecture is presented in Part 2. The motion estimation architecture stores two frames and computes motion vectors for a regular triangular mesh structure as defined by MPEG-4 Part 2.1 The motion estimation architecture uses the block-matching algorithm (BMA) to estimate the vertical and horizontal motion vectors for each mesh node. Parallel and pipelined implementations have been used to overcome the huge computational requirements of the motion estimation process. The two frames are stored in embedded S-RAMs generated with Virage™ Memory Compiler. The proposed motion estimation architecture has been prototyped, simulated and synthesized using the TSMC 0.18 μm CMOS technology. At 100 MHz clock frequency, the proposed architecture processes one CIF video frame (i.e., 352×288 pixels) in 1.48 ms, which means it can process up to 675 frames per second. The core area of the proposed motion estimation architecture is 24.58 mm2 and it consumes 46.26 mW.

Read More: https://www.worldscientific.com/doi/abs/10.1142/S0218126604001921

Mohammed Sayed and Wael Badawy, “A Computational RAM (C-RAM) Architecture for Real-Time Mesh-Based Video Motion Tracking: Part I Motion Estimation,” Journal of Circuits, Systems and Computers, Vol. 13, Issue 6, December 2004, pp. 1203-1216.

A Real-time Multiple-cell Tracking Platform for Dielectrophoresis (DEP) based Cellular Analysis,

There is an increasing demand from biosciences to develop new and efficient techniques to assist in the preparation and analysis of biological samples such as cells in suspension. A dielectrophoresis (DEP)-based characterization and measurement technique on biological cells opens up a broader perspective for early diagnosis of diseases. An efficient real-time multiple-cell tracking platform coupled with DEP to capture and quantify the dynamics of cell motion and obtain cell viability information is presented. The procedure for tracking a single DEP-levitated Canola plant protoplast, using the motion-based segmentation algorithm hierarchical adaptive merge split mesh-based technique (HAMSM) for cell identification, has been enhanced for identifying and tracking multiple cells. The tracking technique relies on the deformation of mesh topology that is generated according to the movement of biological cells in a sequence of images that allows the simultaneous extraction of the biological cell from the image and the associated motion characteristics. Preliminary tests were conducted with yeast cells and then applied to a cancerous cell line subjected to DEP fields. Characteristics, such as cell count, velocity and size, were individually extracted from the tracked results of the cell sample. Tests were limited to eight yeast cells and two cancer cells. A performance analysis to assess tracking accuracy, computational effort and processing time was also conducted. The tracking technique employed on model intact cells in DEP fields proved to be accurate, reliable and robust.

Brinda Prasad, K. Kaler and Wael Badawy, “A Real-time Multiple-cell Tracking Platform for Dielectrophoresis (DEP) based Cellular Analysis,” Measurement Science and Technology, Vol. 6, April 2005, pp. 909-924.

I am the BRAND on online search engines

For the last 10+ years, many companies approached me and promise a better ranking for Google search and to get my link in the first page. This is the goal of many companies, which may be good.

Over the last two weeks, I was building my website and I deployed my experience on website development and social media.

I was able to get my name in all links in the first 2 pages of google search and at least 8 out of 10 links in pages 3 – 12 of the search engine. I am now the brand who can appear 105 times out of 120 result link.

I was able to be dominating the top 27search result out About 130,000 results, It basically demonstrate and I am listed in 134 out of the top 160 and I should conclude that I am the BRAND.

Similar results are achieved on Yahoo and BING, and the following images. The following 17 images prove that my name dominates the top 16 pages search result and the following 2 images show the first pages of Ping and Yahoo search,

Can you do me a favour, search my name “Wael Badawy“ from your end on google.com, yahoo.com and bing.com and write in the comment if you find me that I am the Brand in your search

A new time distributed DCT architecture for MPEG-4 hardware reference model

This paper presents the design of a new time distributed architecture (TDA) which outlines the architecture (ISO/IEC JTC1/SC29/WG11 MPEG2002/M8565) submitted to MPEG4 Part9 committee and included in the ISO/IEC JTC1/SC29/WG11 MPEG2002/9115N document. The proposed TDA optimizes the two-dimensional discrete cosine transform (2-D-DCT) architecture performance. It uses a time distribution mechanism to exploit the computational redundancy within the inner product computation module. The application specific requirements of input, output and coefficients word length are met by scheduling the input data. The coefficient matrix uses linear mappings to assign necessary computation to processor elements in both space and time domains. The performance analysis shows performance savings in excess of 96% as compared to the direct implementation and more than 71% as compared to other optimized application specific architectures for DCT.

Published in:

Circuits and Systems for Video Technology, IEEE Transactions on (Volume:15 , Issue: 5 )

- Page(s):

- 726 – 730

- ISSN :

- 1051-8215

- INSPEC Accession Number:

- 8422879

- DOI:

- 10.1109/TCSVT.2005.846429

- Date of Publication :

- May 2005

- Date of Current Version :

- 02 May 2005

- Issue Date :

- May 2005

- Sponsored by :

- IEEE Circuits and Systems Society

- Publisher:

- IEEE

Alam, M.; Badawy, W.; Jullien, G.; “A new time distributed DCT architecture for MPEG-4 hardware reference model,” IEEE Circuits and Systems for Video Technology, Volume 15, Issue 5, May 2005, pp. 726 – 730.

21 site is infringing my book copyright

I was searching the internet and I found that 21 site is infringing my book copy right including the cover.

If you don’t know me, GOOGLE Me

With he explosion of Digital world, everything is going online.

The Internet is a modern day phone book where people look for services, products, information, news, classes, and any number of other items of interest on a global scale. The Internet is accessible 24/7 through our computers, tablets and smart phones (which means we are always plugged in).

The world has changed. Social media is the way people communicate, advertise, promote and sell. It is the 21st century way of connecting. If you are not using social media to communicate and connect with your business, your business might as well be considered a hobby. Get active on Facebook, Twitter, LinkedIn, Instagram and/or Google+ so your business can thrive and build recognition (there are many other social media sites, but these are the big five). You must have a website. If you have a business and no website. People search the internet, cannot find you so you are do not exist.

People look for everything on the Internet. If you cannot be found within the first couple pages of the search results, it is like you do not exist. People are only going to go to the first or second page but they’re not going to go much further to find you. If they don’t find you, you’ve lost a potential client.

The world has gone digital and there is no escaping it. If you are unsure where to start to build your online presence, call me, email me, sign up on my website. I can help you develop your best-self online so you become recognized for the expert you are.

So, if you don’t know Me, please GOOGLE “Wael Badawy” and let me know.

RAPID PROTOTYPING OF DIGITAL SYSTEMS: A TUTORIAL APPROACH

By James O. Hamblen and Michael D. Furman, Kluwer Academic Publishers, 2000.

This book provides an exciting and chal- lenging laboratory component for an un- dergraduate student as well as design engineers working in industry. It intro- duces the field programmable logic device (FPLD) technology and logic synthesis us- ing CAD tools. The book is organized in 13 chapters as follows. Chapter 1 provides a tutorial for CAD tools that covers the de- sign entry, simulation, and hardware im- plementation using an FPLD. Chapter 2 provides an overview of the UP1 FPLD de- velopment board, where the features of the board are briefly described. Chapter 3 introduces the programmable logic tech- nology where the most common complex programmable logic device (CPLD) and field programmable gate array (FPGA) are presented. Chapter 4 is a tutorial to use both a hierarchical and sequential design with different examples. Chapter 5 de- scribes the UP1core library I/O functions. Chapter 6 introduces the use of VHDL for the synthesis of digital hardware. Chapter 7 describes a state machine that controls a virtual electric train system simulation with video output generated directly by the CPLD. Chapter 8 develops a VHDL model of a simple computer where a fetch, decode, and execute cycle is simulated.

CIRCUITS & DEVICES s NOVEMBER 2001

39 s

Chapter 9 describes how to design an FPLD-based digital system to output VGA video. Chapter 10 describes the PS/2 key- board operation and presents interface ex- amples for integration in designs on the UP1 board. Chapter 11 describes the PS/2 mouse operation and presents interface examples for integration in designs on the UP1 board. Chapter 12 develops a design for an adaptable mobile robot using the UP1 board. Chapter 13 describes a single clock cycle model of the MIPS RISC pro- cessor. The book also includes a large number of laboratory problems and a vari- ety of design projects at the end of each chapter.

The book comes with the new student version of Altera’s MAX+PLUS II CAD tool and the UP1 board is available from Altera at special student pricing.

This is an ideal book for undergraduate digital logic and computer design courses with more than 40 fully developed and simulated examples that can be used on the UP1 board.

MPEG-4 for Multimedia Streaming

Wael Badawy, “MPEG-4 for Multimedia Streaming” Circuit Cellar, December 2001, pp. 36-40.